【高云GW5AT-LV60 开发套件试用体验】 LVDS屏显示和camera

2025-06-21

实现将SC130GS采集的黑白图像数据缓存进DDR3,并以1024*600@60的视频时序输出到LVDS

屏幕显示。其中,DDR3工作频率为600MHz,SC130GS输入的图像数据大小为1280*1024,帧率为

60帧,数据格式为RAW10。

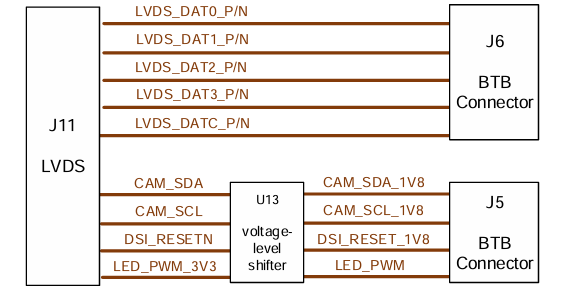

底板提供了一个LVDS显示接口,采用40P 0.5mm间距的FPC连接 器,包含5对差分信号和6个控制信号,分别为4Data+1Clk和I2C、复 位、中断、PWM、使能信号。其中I2C、复位和PWM信号由核心板上 FPGA的4个1.8V电平信号通过底板上的双向电平转换芯片转换为3.3V 电平信号后引出到接口上。LVDS接口连接示意图:

电路原理图如下:

代码分析:

//

//Written by GowinSynthesis

//Tool Version "V1.9.10.02"

//Sat Oct 12 14:33:36 2024

//Source file index table:

//file0 "C:/Gowin/Gowin_V1.9.10.02_x64/IDE/ipcore/DDR/data/ddr_138k.v"

`timescale 100 ps/100 ps

module ddio_lvds (

din,

fclk,

pclk,

reset,

q

)

;

input [6:0] din;

input fclk;

input pclk;

input reset;

output [0:0] q;

wire VCC;

wire GND;

OVIDEO ovideo_gen[0].ovideo_inst (

.Q(q[0]),

.D6(din[6]),

.D5(din[5]),

.D4(din[4]),

.D3(din[3]),

.D2(din[2]),

.D1(din[1]),

.D0(din[0]),

.PCLK(pclk),

.FCLK(fclk),

.RESET(reset)

);

VCC VCC_cZ (

.V(VCC)

);

GND GND_cZ (

.G(GND)

);

GSR GSR (

.GSRI(VCC)

);

endmodule /* ddio_lvds */

1. 模块声明与端口定义

module ddio_lvds (

din, // 7位输入数据(宽度6:0,含D0-D6共7位)

fclk, // 高频时钟(可能为系统时钟或DDR时钟)

pclk, // 并行时钟(可能用于数据锁存或同步)

reset, // 复位信号(高电平有效?需结合IP核特性)

q // 1位LVDS输出(可能为差分信号的正极)

);

- 核心功能:将 7 位并行输入数据

din转换为单路 LVDS 格式输出q,适用于高速串行数据传输场景(如视频信号、DDR 接口等)。 - 命名规则:模块名

ddio_lvds中,ddio可能指双数据速率输入输出(Dual Data Rate I/O),lvds为低压差分信号,暗示涉及高速串行通信。

关键元件与 IP 核分析

OVIDEO ovideo_gen[0].ovideo_inst (

.Q(q[0]), // 输出LVDS信号(单端,实际可能需配合差分对)

.D6(din[6]), .D5(din[5]), ..., .D0(din[0]), // 7位输入数据

.PCLK(pclk), // 并行时钟(用于锁存输入数据)

.FCLK(fclk), // 高频时钟(可能用于生成串行时钟或数据采样)

.RESET(reset) // 复位信号(控制IP核内部状态机)

);

- OVIDEO IP 核功能:

- 通常用于视频数据的串化(Parallel to Serial)或 LVDS 驱动,可能集成并串转换、时钟分频、预加重等功能。

- 7 位输入数据

din[6:0]可能对应视频信号的 RGB565 格式(如 D6-D0 对应 G [5:0] 或类似组合),或自定义协议的并行数据。

- 时钟关系:

-

pclk为并行数据的同步时钟,fclk为高频串行时钟(通常为pclk的倍数,如 2x、4x 等,用于实现高速串行输出)。 - 若

fclk是pclk的 8 倍,则可能实现 8b/10b 编码或类似的串化逻辑。

-

电源与接地元件

VCC VCC_cZ ( .V(VCC) ); // 电源实例化

GND GND_cZ ( .G(GND) ); // 接地实例化

- 显式实例化电源和地,可能是工具自动生成的模板代码,确保综合时电路完整性。

全局置位 / 复位(GSR)

GSR GSR ( .GSRI(VCC) ); // 全局复位使能(高电平有效)

- 用于初始化 FPGA 内部寄存器,确保上电时所有触发器进入已知状态,是可综合设计的常见结构。

信号流向与时序逻辑

din[6:0](并行输入) → OVIDEO IP核 → 串化处理 → q[0](LVDS单端输出)

- IP 核内部可能包含:1、并行数据缓存寄存器(由

pclk驱动);2、串化器(Serializer)将 7 位数据转换为串行流;3、LVDS 驱动器(如差分缓冲器)生成符合 ANSI-644 标准的信号

时钟域处理

- fclk和pclk可能属于不同时钟域,IP 核内部需处理跨时钟域(CDC)问题,例如通过 FIFO 或握手信号同步。

- 若fclk是pclk的整数倍,可能通过锁相环(PLL)生成,确保时钟同步。

复位逻辑

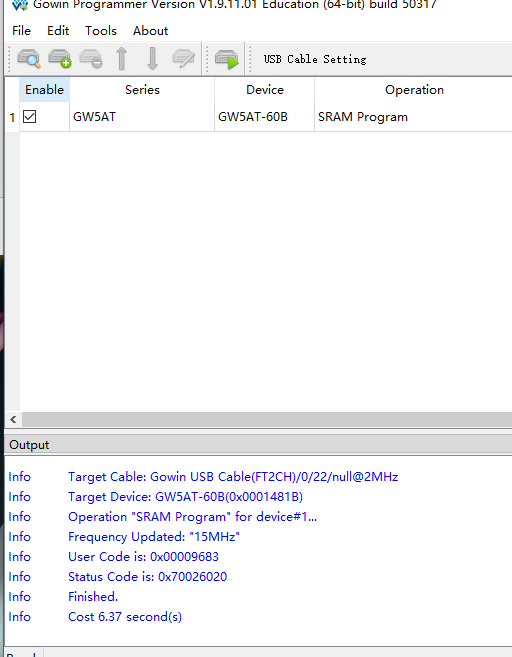

编译下载固件如下:

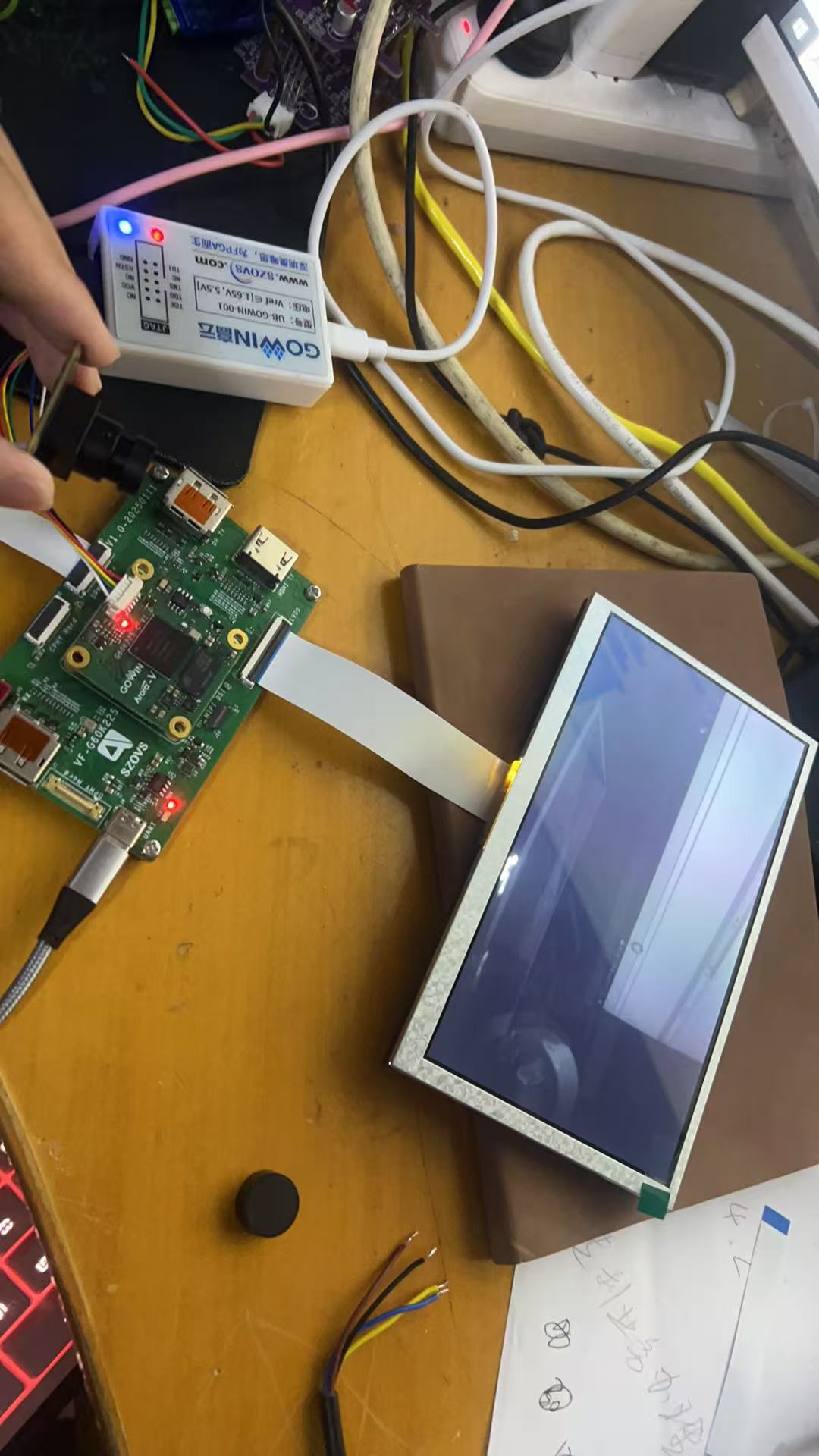

实际效果如下:

实际图 摄像头数据传输到显示屏

摄像头数据传输到显示屏

潜在应用场景

1. 视频传输系统

- 将 RGB565 格式的 7 位视频数据(如 G [5:0] + R [0] 或类似组合)转换为 LVDS 串行流,用于驱动显示屏或摄像头接口(如 MIPI D-PHY 的简化版)。

2. DDR 接口扩展

- 结合

ddio(双数据速率)特性,可能用于 FPGA 与 DDR 存储器之间的接口逻辑,实现高速数据读写(如 DDR3/DDR4 的控制信号传输)。

3. 工业总线通信

- LVDS 的低噪声、高速特性适用于工业总线(如 RS-422、自定义串行协议),传输传感器数据或控制指令。

设计注意事项

1. LVDS 的差分特性

- 当前代码仅输出单端信号

q[0],实际应用中需搭配差分对(如q_p和q_n),可能需修改模块端口或 IP 核配置。

2. 时钟频率匹配

- 需确保

fclk和pclk的频率关系满足 IP 核要求(如fclk = 8 * pclk),否则可能导致数据采样错误或串化失败。

3. 时序约束

- 综合后需添加时序约束(如时钟周期、输入输出延迟),特别是跨时钟域路径,避免出现建立 / 保持时间违规。

4. 复位有效性

- 确认

reset信号的极性(当前代码未明确,但GSR实例化中GSRI=VCC可能暗示复位信号为高电平有效),需与 IP 核文档一致。